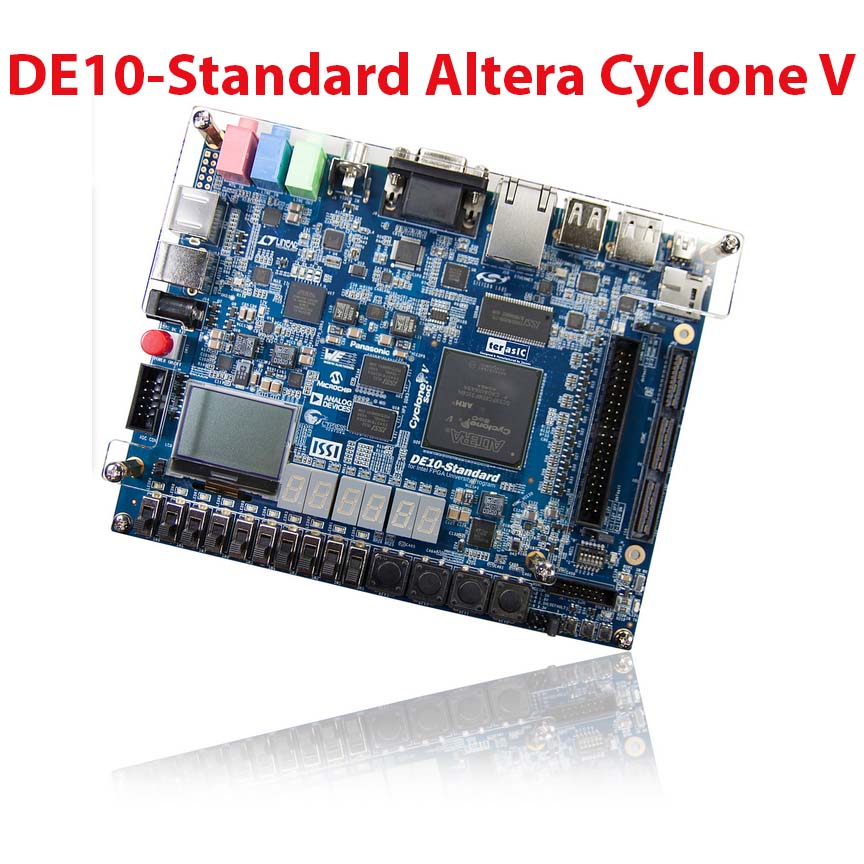

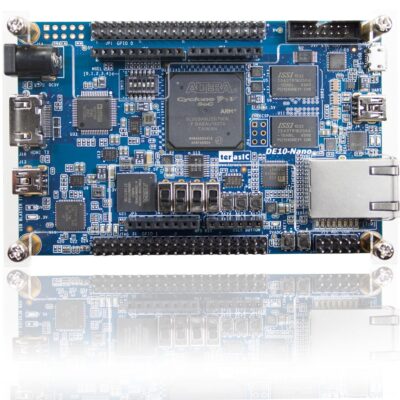

Kit FPGA DE10-Standard Altera Cyclone V SoC

Description

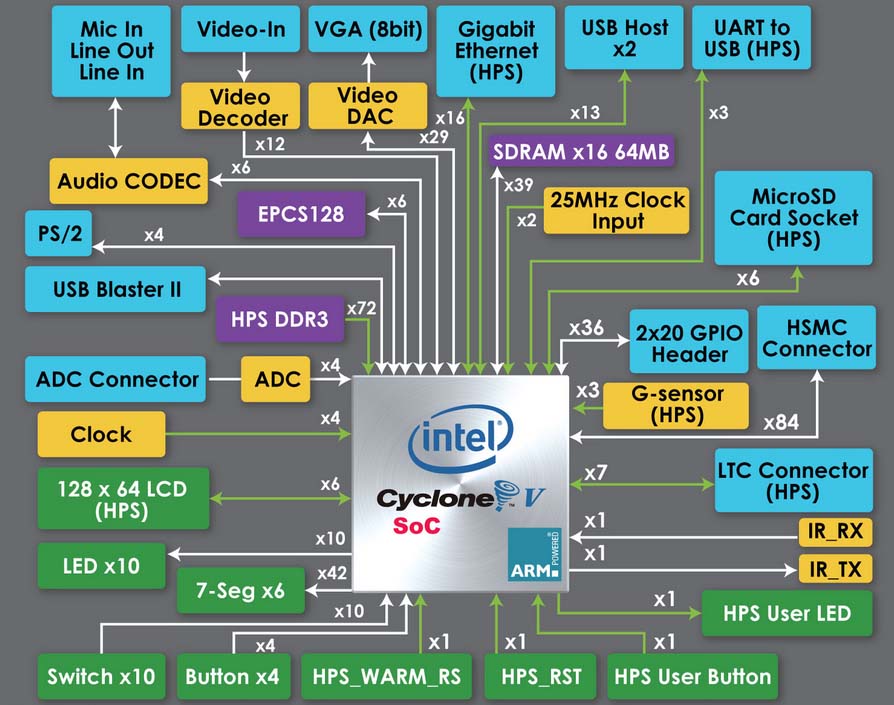

Le kit de développement standard DE10 présente une plate-forme de conception matérielle robuste construite autour du FPGA Intel System-on-Chip (SoC), qui combine les derniers cœurs intégrés Cortex-A9 à double cœur avec une logique programmable de pointe pour une flexibilité de conception ultime. Les utilisateurs peuvent désormais tirer parti de la puissance d’une énorme capacité de reconfiguration associée à un système de processeur hautes performances et basse consommation. Le SoC d’Altera intègre un système de processeur dur (HPS) basé sur ARM composé d’un processeur, de périphériques et d’interfaces mémoire liés de manière transparente à la structure FPGA à l’aide d’une dorsale d’interconnexion à large bande passante. La carte de développement DE10-Standard comprend du matériel tel qu’une mémoire DDR3 haute vitesse, des capacités vidéo et audio, un réseau Ethernet et bien plus encore.

Dispositif FPGA

SoC Cyclone V SX—5CSXFC6D6F31C6N

110K LE, 41509 ALM

Mémoire embarquée de 5 761 Kbits

6 PLL FPGA et 3 PLL HPS

2 contrôleurs de mémoire dur

Système de processeur dur basé sur ARM (HPS)

Processeur MPCore ARM Cortex-A9 double cœur 925 MHz

512 Ko de cache L2 partagé

64 Ko de RAM Scratch

Contrôleur SDRAM multiport avec prise en charge de DDR2, DDR3, LPDDR1 et LPDDR2

Contrôleur d’accès direct à la mémoire (DMA) à 8 canaux

Configuration et débogage

Dispositif de configuration série – EPCS128 sur FPGA

USB Blaster II intégré (connecteur USB de type B normal)

Dispositif de mémoire

64 Mo (32Mx16) SDRAM sur FPGA

1 Go (2x256Mx16) SDRAM DDR3 sur HPS

Prise de carte MicroSD sur HPS

Communication

Deux ports hôtes USB 2.0 (interface ULPI avec connecteur USB de type A) sur HPS

USB vers UART (connecteur micro USB de type B) sur HPS

Ethernet 10/100/1000 sur HPS

Souris/Clavier PS/2

Émetteur/récepteur infrarouge

Connecteurs

Un connecteur d’extension à 40 broches (niveaux de tension : 3,3 V)

Un connecteur HSMC (normes d’E/S configurables 1,5/1,8/2,5/3,3 V)

Un en-tête d’entrée ADC à 10 broches

Un connecteur LTC (un maître d’interface périphérique série (SPI), une interface I2C et une interface GPIO) sur HPS

Afficheur

CNA VGA 24 bits

Module LCD 128 × 64 points avec rétroéclairage sur HPS

l’audio

CODEC 24 bits, prises d’entrée de ligne, de sortie de ligne et d’entrée microphone

Entrée vidéo

Décodeur TV (NTSC/PAL/SECAM) et connecteur d’entrée TV

ADC

Taux d’échantillonnage : 500 KSPS

Numéro de canal : 8

Résolution : 12 bits

Plage d’entrée analogique : 0 ~ 4,096 V

Commutateurs, boutons et indicateurs

4 clés utilisateur (FPGA x4)

10 commutateurs utilisateur (FPGA x10)

11 LED utilisateur (FPGA x10 ; HPS x 1)

2 boutons de réinitialisation HPS (HPS_RST_n et HPS_WARM_RST_n) Affichage 7 segments x6

Capteurs

Capteur G sur HPS

Alimentation

Entrée 12 V CC

Avis

Il n’y a pas encore d’avis.