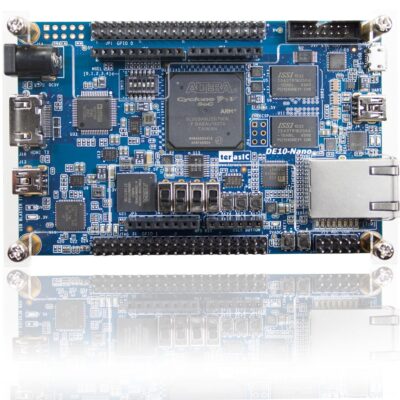

Kit FPGA DE0-Nano Altera Cyclone IV

In Stock

1,800.00د.م.

In Stock

Ajouter à la liste de souhaits

CompareAjouter à la liste de souhaits

Description

La carte DE0-Nano présente une plate-forme de développement FPGA compacte adaptée au prototypage de conceptions de circuits telles que les robots et les projets « portables ». La carte est conçue pour être utilisée dans l’implémentation la plus simple possible, ciblant le circuit Cyclone IV avec un maximum de 22 320 éléments logiques.

Les avantages de la carte DE0-Nano incluent sa taille et son poids, ainsi que sa capacité à être reconfigurée sans matériel superflu. Ces caractéristiques la distinguent des autres cartes de développement à usage général.

Tous les fichiers de conception du microcontrôleur Propeller à 8 noyaux de Parallax sont en code source libre.

- Altera Cyclone IV EP4CE22F17C6N FPGA, 22 320 éléments logiques, mémoire de 594 Ko, 66 multiplicateurs, 4 PLL, 153 broches E/S maximum

- Mémoire flash de configuration 64 Mo

- Oscillateur d’horloge 50 MHz

- 32 Mo SDRAM

- EEPROM I2C 2 ko

- Accéléromètre ADXL345 3 axes

- ADC128S022, 8 canaux, convertisseur A/N 12 bits, 50 à 200 kéch

- 8 x LED vertes

- 2 boutons-poussoirs antirebond

- 4 interrupteurs DIP

- Alimentation : connecteur mini-USB (5 V), deux broches d’embase GPIO (5 V), embase d’alimentation externe 2 broches (de +3,6 à +5,7 V)

- Circuit intégré USB-Blaster pour la programmation

- Deux embases 40 broches offrant 72 broches d’E/S numériques

- Une embase 26 broches offrant 16 broches d’E/S numériques et 8 broches d’entrée analogiques

Avis

Il n’y a pas encore d’avis.